Навигационная цепочка "где я сейчас?" - траектория от главной до текущей страницы сайта. Breadcrumbs.

Передовица (меню разделов)

⇓

Документы

⇓

Штатная документация

⇓

Агат-9 Книга 2

Агат-9 Книга 2

Описание аппаратных средств. Фг3.032.002 ТО5.

Фактически, это описание системной (материнской) платы "Агат-9". Однако, так как в этой версии машины на системной плате был расположен как основной объём оперативной памяти так и микропроцессор, в этом тексте приводится подробное описание системы команд ЦПУ. В то же время здесь совсем не упомянута прочая периферия: контроллеры параллельного порта и дисководов. Отчасти эта книга повторяет ЯБ3.089.026 ТО, но в нём другая компоновка. Есть и другие отличия, например, хуже описаны таймерные прерывания.

Версия 1988 года (ЛЭМЗ ?): DJVU, вес 5.1 Мб - "Лишь бы читалось" и 16 Мб - "Хорошее качество".

Версия 1991 года (ЗЭМЗ): DJVU в цвете - 19 Мб и в монохроме - 2.5 Мб.

Версия 1991 года (ЗЭМЗ): НИЖЕ, ХТМЛ оформлен как печатная версия. Тут только часть книги.

УТВЕРЖДЕН

Фг3.032.002 ТО5-ЛУ

ОКП 40 1370 0012 06

МАШИНА ВЫЧИСЛИТЕЛЬНАЯ ЭЛЕКТРОННАЯ

ПЕРСОНАЛЬНАЯ "АГАТ"

Техническое описание

Часть 6

Описание аппаратных средств

Фг3.032.002 ТО5

СОДЕРЖАНИЕ

1. Введение

2. Основные технические данные ПЭВМ "АГАТ" исполнения 9

3. Обзор технических средств

3.1. Составные части ПЭВМ "АГАТ" исполнения 9

3.2. Конструктивная реализация

3.3. Структурная организация

4. Устройство и работа ПЭВМ "АГАТ"

4.1. Микропроцессор

4.1.1. Основные положения семейства микропроцессоров MCS650X

4.1.2. Технические характеристики микропроцессора

4.1.3. Выводы управления микропроцессора

4.1.4. Выполнение команд

4.2. Организация памяти

4.2.1. Распределение адресного пространства микропроцессора

4.2.2. Распределение памяти

4.2.3. Расширение памяти

4.2.4. ПЗУ и псевдо-ПЗУ

4.3. Дисплейный контроллер

4.3.1. Режимы отображения информации

4.3.2. Отображение информации в режиме "АГАТ"

4.3.3. Отображение информации в режиме Apple ][

4.3.4. Переключение режимов отображения ДК

4.3.5. Переключение цветовой палитры

4.4. Внутренний системный интерфейс

4.4.1. Состав и назначение линий интерфейса

4.4.2. Электрические требования к модулям расширения

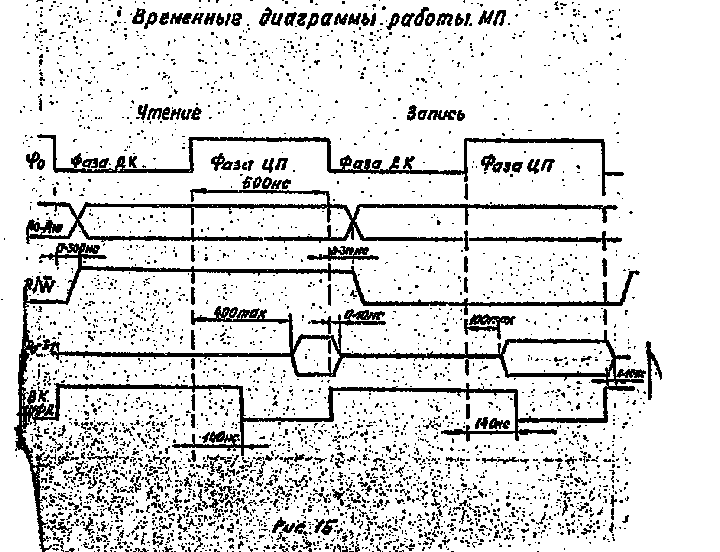

4.4.3. Функционально - временные характеристики

4.4.4. Требования к конструктивной реализации модулей расширения

4.5. Встроенный интерфейс ввода/вывода

4.5.1. Интерфейс клавиатуры

4.5.2. Интерфейс магнитофона

4.5.3. Интерфейс пультов

4.5.4. Встроенный громкоговоритель

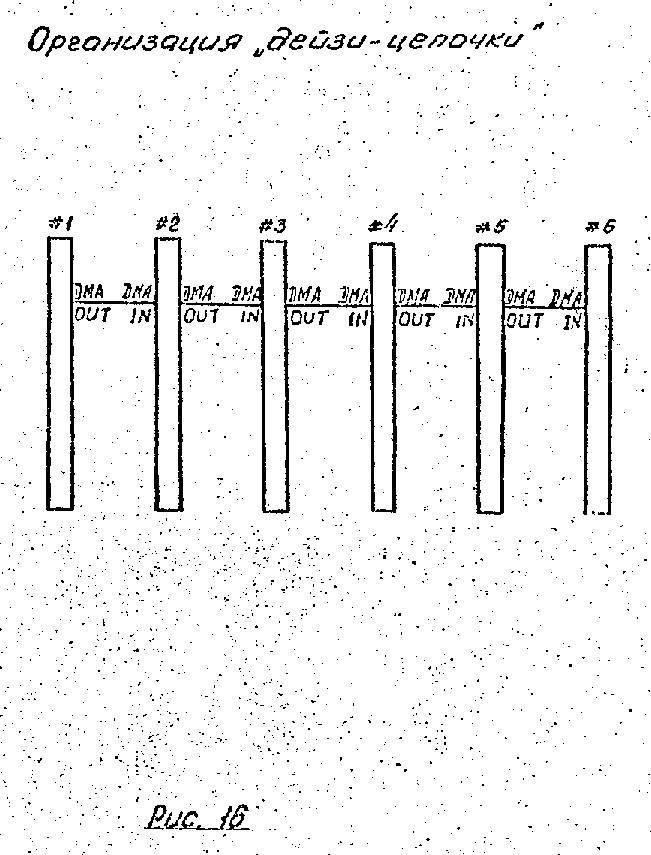

4.6. Прямой доступ к памяти

4.6.1. Организация ПДП

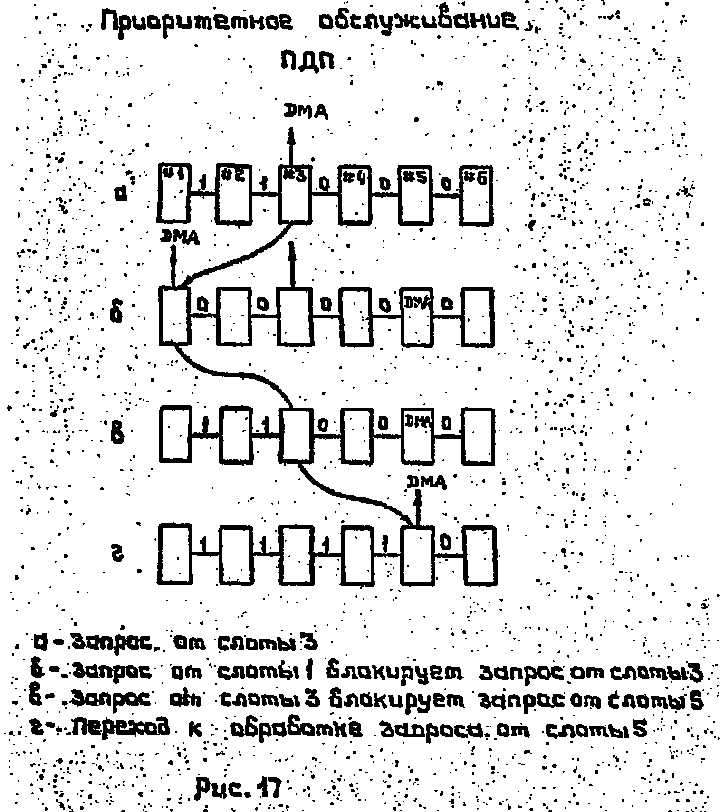

4.6.2. Организация приоритетного обслуживания ПДП

4.7. Прерывания

4.7.1. Запрос прерывания - IRQ

4.7.2. Немаскируемое прерывание - NMI

4.7.3. Временные соотношения обработки прерываний

4.7.4. Таймерные прерывания

Приложение 1. Краткое изложение процедуры выполнения команд

Приложение 2. Время выполнения команд в машинных тактах

Приложение 3. Условные обозначения и сокращения

1. ВВЕДЕНИЕ

Настоящее техническое описание предназначено для изучения структурной организации, принципа работы и назначения аппаратных средств ПЭВМ "АГАТ" исполнения 9 (далее ПЭВМ).

При изучении данного ТО следует дополнительно руководствоваться следующими документами:

Фг3..032.002 ТО Техническое описание. Часть 1.

Общее руководство по работе с ПЭВМ "АГАТ".

Фг3. 032.002 ТО6 Техническое описание. Часть 7.

Программное обеспечение.

Фг3. 032.002 ТО7 Техническое описание. Часть 8.

Программирование аппаратных средств.

2. ОСНОВНЫЕ ТЕХНИЧЕСКИЕ ДАННЫЕ ПЭВМ "АГАТ" ИСПОЛНЕНИЕ 9

2.1 Объем оперативной памяти:

128К байт - минимальный;

640К байт - максимальный при использовании ячеек Фг3.089.170

2.2 Объем ПЗУ:

2К байт - минимальный;

12К байт - максимальный.

2.3 Центральный процессор - СМ630Р с системой команд Микропроцессора MC6502

Количество команд - 56

Режимов адресации - 13

Тактовая частота - 1,021 МГц

Быстродействие - более 500 000 коротких оп/с (510725).

Адресное пространство - 64 Кбайт (16 разрядов адреса).

Обрабатываемое слово данных - 1 байт (8 разрядов).

2.4 Число линий прерывания - 2: маскируемое и немаскируемое;

2.5 Прямой доступ к памяти - имеется: максимальная скорость обмена 1М байт/с.

2.6 Режим работы дисплейного контроллера: - режим "АГАТ" и режим "Apple".

Формат изображения при выводе информации на экран ВКУ в режиме "АГАТ":

Графический монохромный высокого разрешения 256х256 точек;

Графический монохромный с двойной плотностью 512х256 точек;

Графический цветной 256х256 , 4 цвета;

Графический среднего разрешения 128х128 блоков , 8 цветов;

Текстовые 32 строки по 32 цветных символа ( 8 цветов ) или 32 строки по 64 символа (монохромное изображение).

Формат изображения в режиме "Apple":

Графический 280х192 , 6 цветов;

Текстовый 24 строки по 40 символов , монохромный ;

Смешанный - графика 280х160 точек и 4 строки текста.

Цветной графический режим 256х256, монохромный графический режим 512х256,

И фон текстовых режимов реализованы с 4-я цветовыми палитрами.

Подключение видеоконтрольного устройства :

Цветного - через разъем RGB ;

Черно-белого через разъем ВИДЕО.

2.7 Обмен с клавиатурой - последовательный , совместимый с КОИ-8 по ГОСТ 19768-74

2.8 Обмен с накопителем на магнитной ленте - частотно-модулированный, скорость 500 бод.

2.9 Число свободных разъемов для установки дополнительных модулей (слот) - 5.

3. ОБЗОР ТЕХНИЧЕСКИХ СРЕДСТВ

3.1 Составные части ПЭВМ "АГАТ" исполнение 9 Базовый комплект ПЭВМ состоит из : Системного блока - Фг3.038650-01; допускается замена на МЦО 038 005 Блока клавиатуры - Фг3.038.649; Видеомонитора (монохромного) "Электроника МС 6105-01" - БК0.305.072; Пультов аналого-цифровых - Фг3.057.017. В свою очередь, в базовый комплект системного блока входят: Блок питания - Фг2.087.054 или РВИЖ 436.615.001. Объединительная плата процессора, памяти и интерфейса - ЯБ3.089.026-01 или РВИЖ 467444.001 Ячейка контроллера НГМД - ЯБ3.089.023-01; НГМД ЕС 5323.01 или FD-55 (Япония).

3.2. Конструктивная реализация.

Минимально необходимой для функционирования ПЭВМ основой является объединительная плата - печатная плата размером 320х270х25 мм с размещёнными на ней электрорадиокомпонентами, устанавливаемая в нижней части системного блока. На ней реализованы главные функциональные элементы любой ЭВМ: центральный процессор, постоянная память, опертивная память, устройства ввода/вывода, дисплейный контроллер (как функциональный элемент впервые появился в персональных ЭВМ). Кроме того, на объединительной плате установлены 6 специальных многоконтактных разъёмов, предназначенных для ввода дополнительных аппаратных средств расширения функциональных возможностей: дополнительной памяти, контроллеров переферийных устройств, интерфейсов ввода/вывода, контроллеров АЦП и ЦАП, со - процессоров и других специализированных средств и узлов вычислительной техники. Все дополнительные средства расширения реализуются в виде ячеек или модулей - печатных плат размером 240х140х15 мм с размещёнными на них электрорадиокомпонентами, разъёмной вставкой для подключения к слоте расширения и, если необходимо, разъёмами для подключения внешних устройств: принтеров, плоттеров, внешних ЗУ, датчиков и прочих периферийных устройств.

3.3. Структурная организация.

В основе структурной организации ПЭВМ "АГАТ" лежит "открытая архитектура" - принцип построения персональных компьютеров, впервые реализованный в ПЭВМ "Apple II". "Открытая архитектура" персонального компьютера предполагает максимальную ориентацию всех его технических средств на представление возможности пользователю самому определять желаемую конфигурацию системы, в зависимости от требований и специфики области применения или конкретных задач пользователя. Вэтом случае, такой первоначально приобретённый компьютер становится лишь минимально необходимой основой для дальнейшего развития аппаратных средств, по мере определения потребностей пользователя и появления новых задач.

- Открытая архитектура обязывает персональный компьютер иметь:

- несколько слот расширения, в качестве основы для реализации внутреннего системного интерфейса;

- соответствующую конструкцию, максимально удобную для простой и быстрой переустановки нужных пользователю модулей расширения;

- блок питания, способный в достаточной широких пределах "не замечать" изменений нагрузки по питающим напряжениям;

- аппаратные средства, способные различать установленные модули и поддерживать сигналы внутреннего системного интерфейса в заданных пределах, даже при полной загрузке всех слот расширения;

- программные средства, способные управлять всеми возможными дополнительными аппаратными средствами установленных модулей.

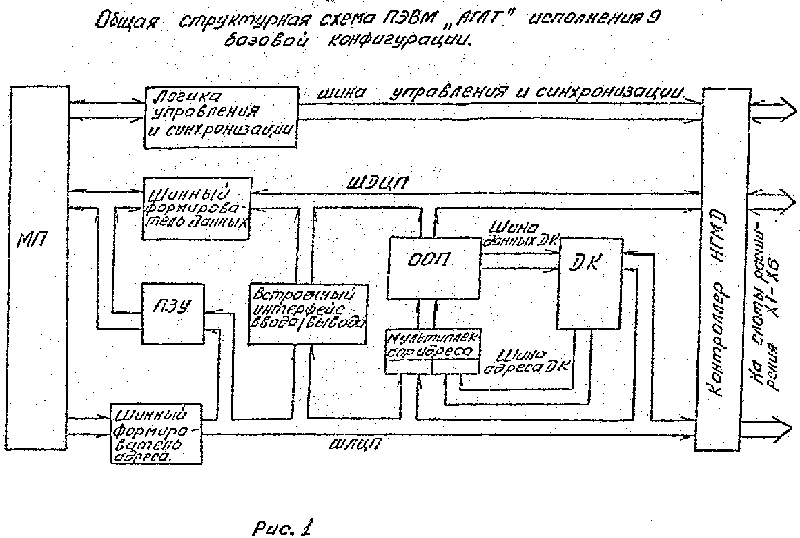

Общая структурная схема ПЭВМ приводится на рис. 1. Следует отметить, что все минимально необходимые для реализации ПЭВМ с открытой архитектурой аппаратные средства реализованы на объединительной плате: микропроцессор, оперативная память, дисплейный контроллер, встроенный интерфейс ввода/вывода, внутренний системный интерфейс.

4. УСТРОЙСТВО И РАБОТА ПЭВМ "АГАТ"

4.1. Микропроцессор.

Центральным элементом, "сердцем", любой микрокомпьютерной системы является микропроцессор. Во всех исполнениях ПЭВМ "АГАТ" используется микропроцессор совместимый с микропроцессорами известными, как 6502 и получившими наиболее широкое распространение в персональных домашних компьютерах благодаря усилиям таких фирм как Apple Computer, Atary, Commodore и др. Первоисточником для всех последующих версий микропроцессоров 6502 известных в настоящее время послужил микропроцессор MCS6502 - второй член микропроцессорного семейства MCS650X фирмы MOS Technology. Поэтому в дальнейшем описании излагаются все основные положения этого семейства, которые в полной мере распространяются и на микропроцессор испольуемый в ПЭВМ "АГАТ".

4.1.1. Основные положения микропроцессорного семейства MCS650x.

Микропроцессорные системы использующие любой из микропроцессоров семейства MCS650x или аналогичных им, организуются вокруг двух основных шин. Каждая шина содержит набор параллельных трактов для передачи двоичной информации между устройствами системы. Первая - адресная шина - является однонаправленной и используется для передачи адреса, образуемого микропроцессором. 16 линий шины адреса позволяют процессору иметь непосредственный доступ к 65536 (64К) ячеек образующих адресное пространство микропроцессора. Всё адресное пространство разбивается на 256 страниц по 256 адресов каждая, при этом 16 линий шины адреса разделяются на два байта: старший байт задаёт номер адресной страницы, а младший - номер ячейки в пределах этой страницы. Понятие адресной страницы (далее - страницы) занимает особое место в семействе 650х (например, существует даже тип адресации присущий только этому семейству - адресации с помощью нулевой страницы), и его не следует путать с понятием экранная страница, определяющим область памяти отображаемой на экране.

В отличии от адресной, шина передачи данных или шина данных является двунаправленной, имеет 8 линий и в процессе операции "запись" передаёт данные из микропроцессора, а в ходе операции "чтение" принимает данные в микропроцессор. Традиционно для фон - Неймановской архитектуры процессоров в семействе 650х все данные и все команды пересылаются по шине данных.

Направление передачи данных определяется линией R/W (чтение/запись) в микропроцессоре. Пока сигнал по линии R/W идёт высоким уровнем, выполняются операции чтения и информация по шине данных поступает в микропроцессор. Сигнал на этой линии становится низким только тогда, когда микропроцессор выполняет операции записи и выставляет данные на шину данных.

Синхронизация работы микропроцессора и всех передач данных может быть осуществленна посредством всего одного сигнала основной тактовой частоты системы. Существует несколько характерных особенностей синхронизации микропроцессоров семейства 6502, отличающих их от других известных семейств, например, от микропроцессоров фирмы Intel (8080, 8085, 8086, 8088 и др.). Кратко эти особенности иожно сформулировать в виде следующих положений:

Один период"один такт"одна операция"один цикл.

Каждый период тактовой частоты определяется как машинный такт, за который выполняется одна законченная микрооперация из составляющих текущую выполняемую команду. При этом каждый машинный такт представляет собой цикл памяти, втечении которого память читается или записывается, одновременно с выполнением внутренних операций в микропроцессоре, в том случае, если микропроцессор должен выполнить какие - либо внутренние действия занимающие весь машинный такт, но не задействующие внешнюю информационную шину, то данные считываемые из памяти игнорируются.

Разделение фазы.

Каждый машинный такт разделяется на две равные части(фазы) длительностью по полпериода каждая (рис. 2). Все передачи данных осуществляются только втечение фазы с высоким уровнем сигнала ФО. Когда ФО идёт низким уровнем, микропроцессор выполняет внутренние операции, одновременно осуществляя переустановку кода на адресной шине, и шиной данных не пользйутся. Это обстоятельство позволяет на время действия низкого уровня сигнала ФО задействовать оперативную память для обслуживания других пользователей ОП, например дисплейного контроллера, без какой - либо задержки микропроцессора.

Конвейерная (магистральная) обработка.

Принцип конвейерной обработки предполагает перекрытие действий при выполнении команд, например, когда завершающие действия текущей команды внутри микропроцессора одновременно сопровождаются выборкой и интерпретацией очередной команды. Для иллюстрации данного положения далее рассматривается выполнение команды ADC (сложить с переносом) с использованием абсолютной адресации (содержимое аккумулятора сложить с содержимым ячейки памяти, адрес которой содержится в двух последующих байтах).

Такты Внешняя операция Адрес Данные Внутренние операции

1 Выборка хода команды 100 ADC Наращивание Р - счётчика до 101

2 Выборка младшего байта 101 ADL Наращивание Р - счётчика до 102,

адреса из памяти интерпритация команды ADC

3 Выборка старшего байта 102 ADH Наращивание Р - счётчика до 103,

адреса из памяти сохранение ADL

4 Выборка операнда из ADH данные Загрузка данных

памяти +ADL

5 Выборка следующего кода 103 STA Наращивание Р - счётчика до 104,

команды из памяти выполнение ADC команды:А+М+С

6 Выборка адреса из памяти 104 ADL Наращивание Р - счётчика до 105,

пересылка результата в

аккумулятор интерпритации

команды STA

Использованные в примере обозначения:

ADL - младший байт исполнительного адреса;

ADH - старший байт исполнительного адреса;

Р - счётчик - программный счётчик;

А - аккумулятор;

М - содержимое ячейки памяти;

С - перенос;

STA - обозначение команды пересылки содержимого аккумулятора в память.

В первом такте КОП (код операции, код команды) выбирается из памяти по адресу установленному из Р - счётчика. Уже во втором такте одновременно с интерпритацией команды сложения, для выполнения которой требуются, как минимум ещё три обращения к памяти, происходит выборка младшего байта адреса, необходимого для обращения за слагаемым находящимся в памяти. В конце второго такта микропроцессор знает в результате интерпритации абсолютного способа адресации, что из следующей ячейки памяти необходимо извлечь старший байт адреса. В третьем такте извлекается старший байт адреса, а в четвёртом - операнд, по адресу извлечённому во втором и третьем тактах.

До сих пор все действия микропроцессора заключались лишь в подготовке к выполнению команды ADC: все четыре выполненных такта были заполнены только выборками из памяти. Теперь же необходимо завершить команду собственно исполнив её. Но в связи с тем, что действия с памятью для этой команды закончены, в пятом такте, одновременно с выполнением сложения, микропроцессор осуществляет выборку следующей команды. Завершение же команды сложения происходит только в следующем, шестом такте, когда микропроцесор уже интерпретирует новую команду, выбранную в пятом такте, одновременно пересылая результат сложения в аккумулятор. Отсюда следует, что хотя выполнение команды ADC занимает в действительности шесть тактов, с точки зрения выполнение программы она занимает только четыре, т.к. два заключительных такта перекрываются, с выполнением следующей команды.

Таким образом, можно утверждать, с незначительными исключениями, что число тактов, занимаемых камандой, равно числу обращения микропроцессора к памяти. При этом не существует команд занимающих менее двух тактов (циклов), т.к. для выполнения любой команды необходимо по крайней мере два действия: выборка КОПа и его интерпретация

Конкретные требования по синхронизации и условиям обмена информацией между микропроцессором и всеми остальными узлами системы излагаются в п. 4.4.3. Для непосредственной синхронизации работы микропроцессора (МП) используется сигнал тактовой частоты ФО, подаваемый на вход 3.

4.1.2. Технические характеристики микропроцессора.

Адресное пространство 64К адресов (65386)

Адресная шина 16 бит, параллельная

Информационная шина 8 бит, параллельная двунаправленная

Количество команд 56

Способов адресации 13

Напряжение питания +5 В

Рассеиваемая мощность 250 мВт

Тактовая частота 1,021 МГц

Прерывания 2 - маскируемое и немаскируемое

Начальная установка 1 - по линии RESET

Внутренние регистры 1 аккумулятор (А)

2 индексных регистра (Х и Y)

1 указатель стека (SP)

1 состояния процессора (Р)

Стек 256 байт, фиксированный

Быстродействие:

коротких операций более 500 000 оп/с (510725)

пересылки в память более 340 000 оп/с (340483)

4.1.3. Выводы управления микропроцессора.

Кроме выводов занятых шинами адреса и данных, синхронизации и сигналов R/W, у микропроцессора имеется ряд выводов управления предназначенных для остановки, прерывания и начальной установки микропроцессора.

Установка МП в начальное состояние при первом или повторном запуске ПЭВМ осуществляется сигналом RES (Сброс). По спаду уровня этого сигнала микропроцессор останавливается в любом случае независимо от того , какие действия он выполнял в текущий момент. При установлении высокого уровня на линии RES микропроцессор начинает выполнять микропрограмму повторного запуска предопределяющую строгую последовательность его действий на определённый начальный промежуток времени. Для выполнения программы запуска сигнал на входе RES должен находится на низком уровне не менее 8 мкс. Система автостарта, подключённая к нопке "СБР" на клавиатуре, удерживает RES - 0 после включения питания на время достаточное для стабилизации всех входных напряжений и синхросигналов и выполнения микропрограммы запуска.

Сигнал RDY (готовность - контакт 2) позволяет приостановить работу микропроцессора. Установка сигнала RDY в низкий уровень остановит микропроцессор в момент действия Ф1, при этом адресная шина сохраняет адрес текущей ячейки, содержимое которой выбирается.

Сигналы IRQ (контакт 4) и NMI (контакт 6) являются соответственно сигналами запроса прерывания и немаскируемого прерываиня. При низком уровне сигнала IRQ и программном разрешении прерываний микропроцессор по окончании выполнения текущей команды переходит к подпрограмме обработки маскируемого прерывания. По спаду сигнала NMI, независимо от внутреннего состояния, микропроцессор начинает по окончании текущей команды цикл прерывания, передавая управление соответствующей подпрограмме обработки (см. п. 4.7.).

Все линии управления RDY, RES, IRQ, NMI, идущие к микропроцессору входят в состав линий внутреннего системного интерфейса и при необходимости могут использоватся для непосредственного вмешательства в текущую работу микропроцессора различных модулей расширения. При отсутствии активных сигналов на всех этих линиях поддерживается высокий уровень сигнала с помощью резисторов 3,3 кОм, подключённых к цепи +5 В.

4.1.4. Выполнение команд

В этом разделе содержится краткое изложение выполнения команд с указанием состояния микропроцессора, его адресной и информационной шин для каждого такта различных команд. Такое подробное рассмотрение, даёт возможность при необходимости, легко определить, что следует ожидать в ходе выполнения одного шага любой программы. Всю совокупность системы команд можно разбить на несколько типов, имеющие общие признаки при их выполнении. Полностью подробности выполнения всех типов команд в зависимости от возможных вариантов адресации приводятся в приложении1. В приложении 2 приводятся сводные данные по времени выполнения всех команд для всех типов адресации.

4.1.4.1. Однобайтовые команды.

ASL DEX NOP TAX TYA

CLC DEY ROL TAY

CLD INX SEC TSX

CLI INY SED TXA

CLV LSR SEI TXS

Все однобайтовые команды выполняются за два такта. Во втором такте происходит обращение по адресу равному очередному состоянию программного счётчика, но поступающий по шине данных код следующей команды игнорируется, так как ещё не окончено выполнение текущей команды. В следующем такте происходит обращение по тому же самому адресу, но на этот раз код следующей команды микропроцессором воспринимается, расшифровывается и выполняется.

4.1.4.2. Команды с использованием памяти.

ADC CMP EOR LDY

AND CPX LDA ORA

BIT CPY LDX SBC

Эти команды реализовываются путём выполнения операций внутри микропроцессора, с использованием данных, выбранных из исполнительного адреса. Основной особенностью таких команд является то, что в процессе работы программы выполнение таких команд осуществляется за три шага, которые фактически являются подготовительными:

первый шаг (один такт) состоит в выборке кода команды,

второй шаг (от 0 до 4 тактов) представляет собой расчёт дополнительного адреса,

третий шаг - выборка данных из исполнительного адреса.

Собственное же выполнение команды происходит уже в ходе выборки и расшифровки следующей команды.

Особое место в этой группе занимают команды с абсолютной индексированной и косвенной индексированной адресацией, в силу их неоднозначности по времени выполнения. Число тактов занимаемых этими командами зависит от того, происходит или нет пересечение границы страницы в операции индексирования. В том случае, если граница страницы пересекается, то добавляется ещё один такт (в прложении этот такт обозначен скобками), а данные выбираемые в предыдущем такте игнорируются.

4.1.4.3. Команды запоминания.

STA STX STY

Практически эти команды схожи с командами предыдущей группы, отличаясь лишь тем, что вместо выборки данных из памяти выполняется запись (сигнал в линии R /W=0).

4.1.4.4. Команды чтения - модификации - записи.

ASL DEC ROL

LSR INC ROR

Команды чтения - модификации - записи предусматривает считывание операнда из памяти, его модификацию и последующую запись видоизменённых данных по тому же адресу.

4.1.4.5. Смешанные команды.

BCC BCS BEQ

BMI BNE BPL

BVC BVS BRK

JMP RTI PNA PLA

JSR RTS PNP PLP

Конкретные действия осуществляемые при выполнении команд этой группы определяются спецификой каждой из команд, что отражено в соответствующем разделе приложения 1.

4.2. Организация памяти.

Объём имеющейся в наличие физической оперативной памяти только объединительной платы (128 К байт) уже превышает объём адресного пространства микропроцессора (64 К), что не позволяет ему прямо адресоваться к любой части памяти. При использовании дополнительных ячеек расширения оперативной памяти её общий объём может достигать 640 К байт, что ещё больше осложняет задачу обеспечения обращений микропроцессора в пределах доступной оперативной памяти ПЭВМ. Чтобы обеспечить микропроцессору доступ ко всему имеющемуся в наличии объёму оперативной памяти, в ПЭВМ реализована архитектура с гибким распределением памяти, по построению близкая к концепции виртуальной памяти. С этой целью предусматривается преобразование адресов формируемых микропроцессором (логических), в адреса, по которым осуществляется обращение к оперативной памяти (физические). Данные необходимые для такого преобразования хранятся в специальных таблицах текущего распределения памяти. Изменение хранящихся в таблицах данных позволяет произвольно изменять текущее распределение адресов логического пространства в пределах физического. Это позволяет микропроцессору с ограниченным адресным пространством (в 64 К) иметь гибкий доступ к любой зоне оперативной памяти с объектом, превышающий возможности прямой адресации микропроцессора (до 128К и выше при установке модулей расширения оперативной памяти).

Далее оперативная память установленная на объединительной плате будет называтся основной (ООП), а память добавляемая в ПЭВМ за счёт установки дополнительных плат - дополнительной (ДОП).

4.2.1. Распределение адресного пространства микропроцессора.

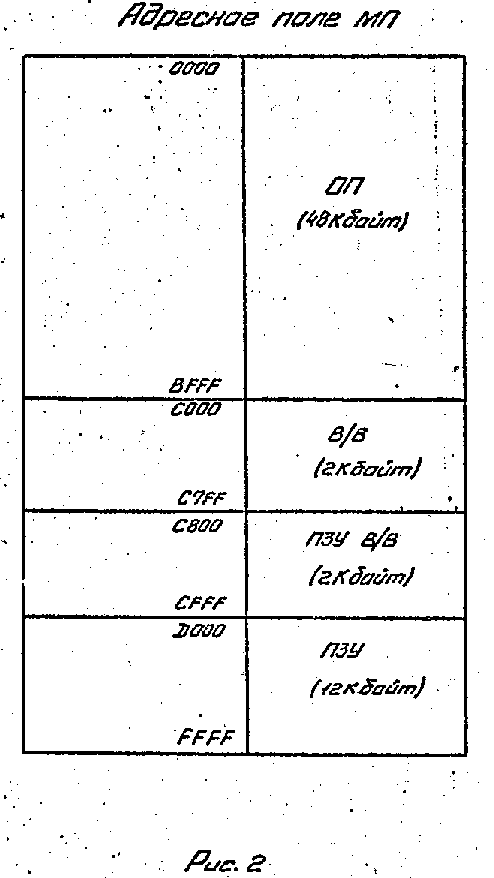

Как уже упоминалось, общее число адресов, доступных для прямого обращения микропроцессора, определяется числом линий шины адреса и составляет 64К (65484) адресов (от 0000 до FFFF в шестнадцатиричной системе исчесления). Особенности функционирования данного типа микропроцессора, а также соображения по обеспечению совместимости, предопределили следующее распределение адресного пространства МП (рис. 2):

адреса 0000 - BFFF (48К) выделены под оперативную память для хранения программ и данных;

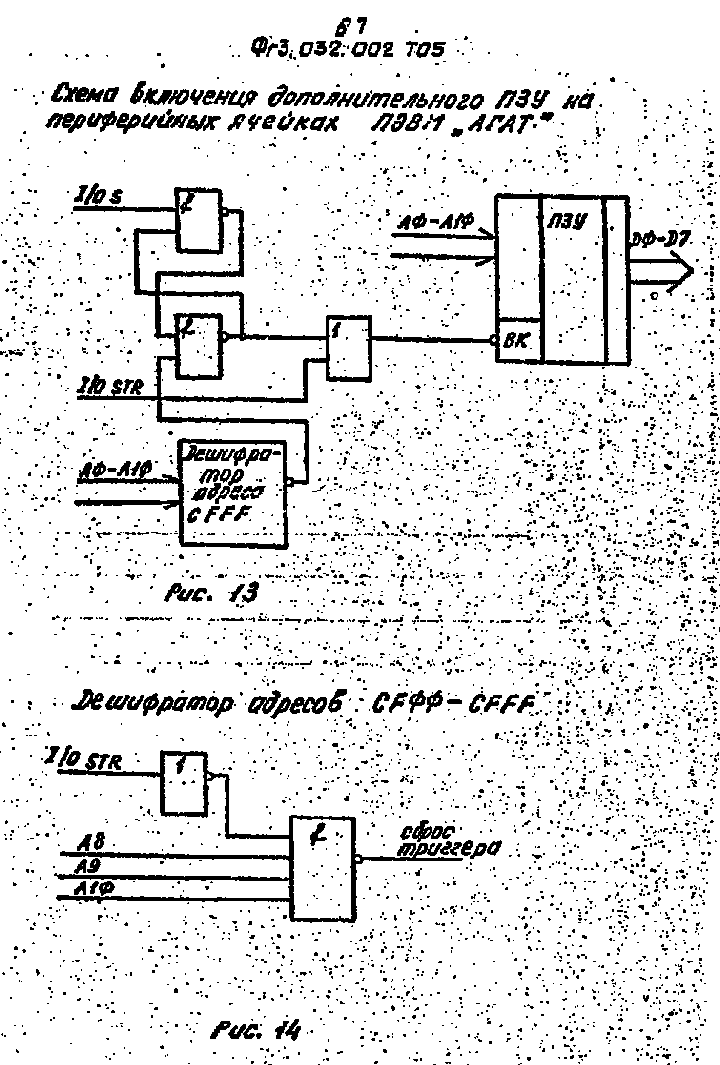

адреса C000 - C7FF (2К) выделены под управление интерфейсом ввода/вывода;

адреса C800 - CFFF (2К) отводятся для ПЗУ ввода/вывода, т.е. для ПЗУ, устанавливаемых на модулях расширения с возможностью доступа к ним через внутренний системный интерфейс;

адреса D000 - FFFF (12К) - область постоянной памяти, которая может быть занята либо стандартными ПЗУ, либо частью ОЗУ в режиме псевдо - ПЗУ (см. п. 4.2.4.). Область адресов F800 - FFFF всегда занята специальной программой "Системный монитор" (далее МОНИТОР).

В адресах отведённых под оперативную память существуют некоторые области, которые ни при каких условиях не могут быть использованы пользователем призвольно. Это области зарезервированы системным программным обеспечением для нормальной работы микропроцессора и под различные системные функции. Прежде всего это фиксированные 4 области занимающие младшие 4 страницы (с 00 по 03) в адресном пространстве микропроцессора.

Нулевая страница.

Занимает самые младшие 256 байт адресного пространства: адреса 0000 - 00FF. Предназначена для реализации специального способа адресации: адресации нулевой страницы. При идентификации кода команды с адресацией нулевой страницы микропроцессору не требуется выполнять накаких действий для определения старшего байта исполнительного адреса, т.к. автоматически предполагается, что он принадлежит младшей адресной странице, т.е. равен 00. Это позволяет исключить один такт при выполнении таких команд и сэкономить один байт памяти необходимой для хранения каждой такой команды. Максимально активное использование команд с адресацией нулевой страницы способствует уменьшению длины программы и сокращению времени её выполнения. Отдельные ячейки нулевой страницы используются и программой "Системный монитор", и дисковой операционной системой, и интерпретатором языка БЕЙСИК, и другими системными программами.

Стек.

Занимает следующие за нулевой страницей 256 байт - адреса 0100 - 01FF. Предназначен для сохранения содержимого внутренних регистров при прерываниях микропроцессора и при его переходах к выполнению программ. При каждой стековой операции микропроцессор автоматически предполагает наличие стека в адресах первой страницы, т.е. устанавливает старший байт исполнительного адреса в состояние 01. Размер стека в 256 байт позволяет осуществить 128 вложенных вызовов программ или 85 прерываний при срхранении содержимого минимального числа внутренних регистров - программного счётчика и регистра состояния. При сохранении содержимого всех внутренних регистров (добавляются аккумулятор и индексные регистры) общее число прерываний не превышает 42.

Входной буфер.

Запоминает 256 байта второй страницы - адреса 0200 - 02FF. Используется большинством программ и языков, как входной буфер для ввода информации, поступающей от пользователя, например, с клавиатуры.

Векторные ячейки.

Эти ячейки специального назначения системного программного обеспечения находятся в пределах третьей страницы - адреса 0300 - 03FF. Например, 16 специальных ячеек с адресами с адресами 03F0-03FF используются программой МОНИТОР при диалоге с пользователем.

Экранная (текстовая или графическая) страница - память экрана.

Это область памяти, используемая в данный момент в качестве памяти экрана, т.е. информация хранящаяся в этой области отображается на экране в одном из возможных режимов отображения.

4.2.2. Распределение памяти.

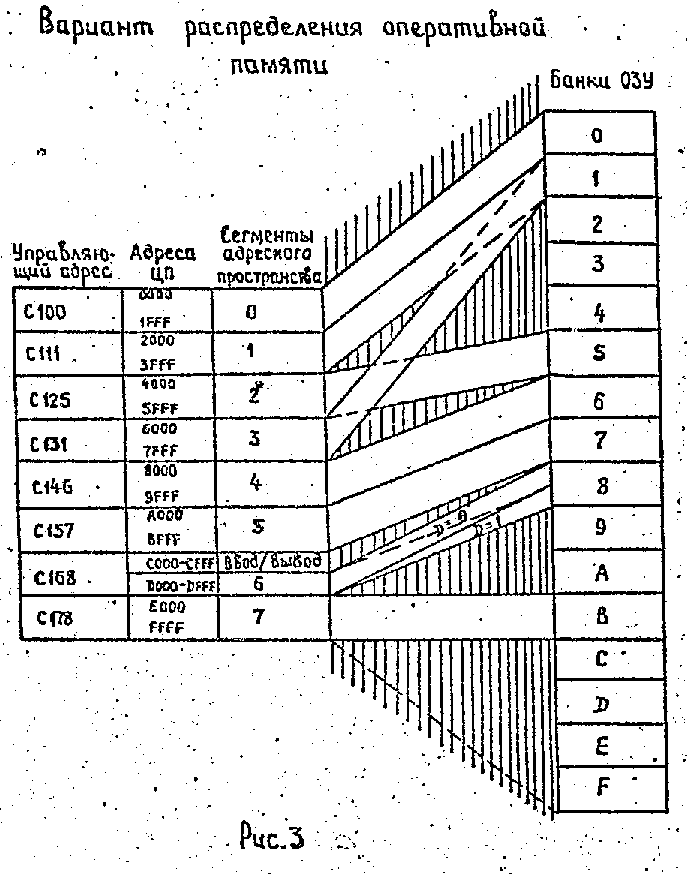

Гибкая архитектура распределения памяти открывает широкие возможности не только для расширения основной оперативной памяти, но и для её свободного перераспределения по желанию программиста при организации различных вычислительных процессов и программ. С целью реализации гибкой архитектуры, как логическое (адресное пространство микропроцессора), так и физическое (совокупность адресов доступной оперативной памяти) адресные пространства разбиваются на области по 8К байт (рис. 3). Области, на которые разбивается физическое адресное пространство, в дальнейшем будут называться "банками", а в области логического адресного пространства - "сегментами". Таким образом всегда имеется 8 сигментов, 16 банков основной оперативной памяти и 16Хр - дополнительной, где р=0 - 4, в зависимости от числа установленных ячеек расширения памяти Фг3. 089. 170.

Все банки эквивалентны друг другу и любой из них может занять любой из 8 сигментов. Шесть младших сигментов (с 0 по 5), занимающие адреса оперативной памяти (0000 - BFFF) равноценны между собой и отличаются только адресами обращения МП. (Однако не следует забывать об особых зонах в нулевом сигменте, описанных в предыдущем разделе, что требует определённой осторожности при переключениях). Сигменты 6 и 7 занимающие адреса ПЗУ D000 - FFFF имеют дополнительные режимы работы, которые характеризуются как псевдо - ПЗУ (см. п. 4.2.4.). Кроме того, имеются дополнительные отличия сигмента 6, заключающиеся в том, что доступ к нему возможен только через адреса D000 - DFF, из-за постоянного и неизменного наличия в адресах C000 - CFFF области ввода/вывода. Поэтому автоматически подразумевается, что банк подключённый к сегменту 6 разделяется на две части по 4К байт, с возможностью подключения каждой из них по правилам, описанным в п. 4.2.4.

Начальное распределение памяти устанавливается программой "Системный монитор", записанной в специальном стартовом ПЗУ объединительной платы, сразу по включении питания ПЭВМ. Оно обеспечивает подключение к нулевому сигменту нулевого банка основной оперативной памяти, к первому сегменту первого банка и т.д.; последние восемь банков с номерами от 8 до F оставляются неподключёнными.

Текущее распределение ОПП задаётся в специальной таблице, которая постоянно хранится в регистрах, реализованных на основе статического ОЗУ, входящего в состав устройства распределения памяти. Каждому сегменту соответствует регистр, при этом номер сегмента соответствует адресу регистра в таблице. Содержимое регистра определяет номер банка, который подключён на место данного сегмента в логическом адресном пространстве. Перераспределение соответствия банков и сегментов осуществляется МП обращением по специальным адресам отведённым в области ввода/вывода - С100 - С1FF. Изменения в таблицу распределения вносятся выполнением операции записи по адресу С1mn, где m - номер сегмента (m=0-7) и n - номер банка (n=0-F).

Содержимое таблицы распределения памяти может быть прочитано по тем же адресам. Для этого ЦП должен выполнить операцию чтения по адресу соответствующего сегмента - 01mX,где X означает любой из 16 адресов 0-F. В результате выполнения такой операции в ЦП по шине данных поступит код mn, т.е. номер банка n занимающего сегмент m: кода номера сегмента m на разряды D4 - D6 ШД ЦП и содержимое регистра указывающее код номера банка, подключенного на данный сегмент на разряды D0-D3.

4.2.3. Расширение памяти.

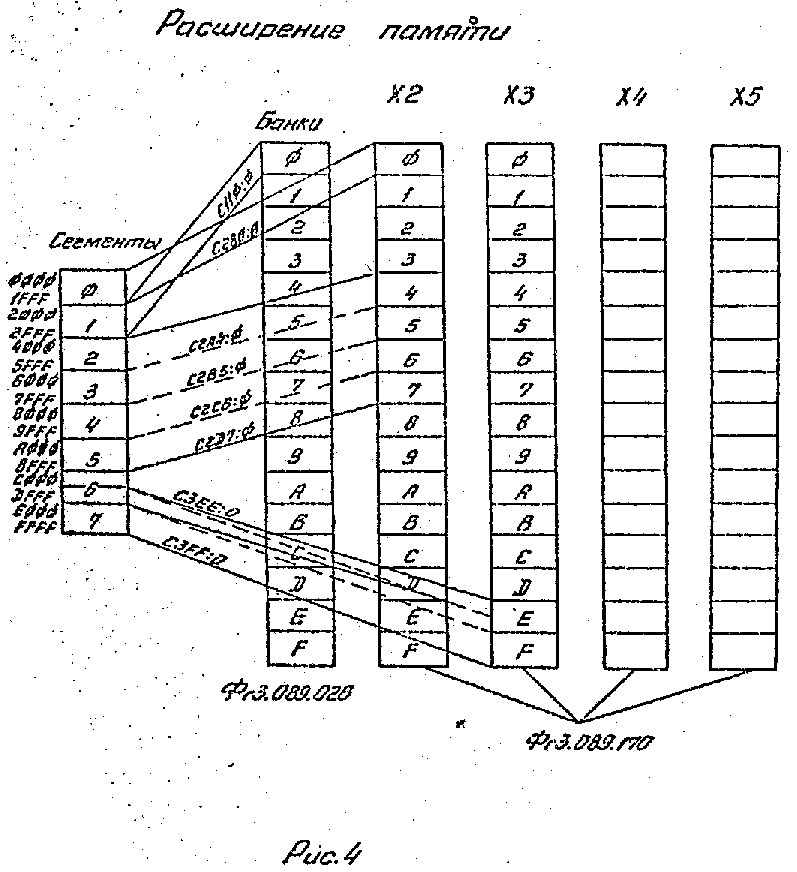

Расширение оперативной памяти возможно с помощью ячеек Фг3. 089. 170., имеющих ёмкость 128К байт. Максимальное число ячеек одновременно установленных в ПЭВМ равно 4, т.е. максимальная общая ёмкость оперативной памяти ПЭВМ равна 640К байт (рис. 4.).

Также как и в ООП, любой из 16 банков ДОП может занять любой из 8 сегментов. Перераспределение соответствия банков и сегментов также как и в ООП осуществляется выполнением команды записи, но по другим адресам. Эти специальные адреса ввода/вывода закреплены за каждой слотой расширения (см. табл. 1) и при необходимости изменения текущего распределения микропроцессор должен сформировать адрес Cqmn, где q=2-5 указывает номер слоты расширения, m=0-7 (разряды А4-А6 ША ЦП) - номер сегмента, а n=0-F - номер банка (разряды А0-А3 ША ЦП). Кроме того необходимо также указать признак активности ДОП на данном сегменте, что не требуется при изменении распределения ООП. Признак активности указывает, что данный сегмент адресного пространства занят соответствующим банком ДОП, а доступ к ООП в пределах данного сегмента заблокирован. Для этого используется старший разряд младшего байта ША ЦП - А7: если необходимо задать активность на данном сегменте данного банка ДОП, то необходимо чтобы был сформирован адрес Cp (m+8)n, т.е. разряд А7 ША ЦП должен быть равен "1".

Текущее распределение ДОП также может быть считано ИП, обращением по любому из адресов соответствующей слоты расширения, т.е. по адресам CqXX, где q=2-5 задаёт номер слоты ДОП.

При использовании более одной ячейки расширения (рис. 4), т.е. когда существует доступ к ДОП: чем выше номер слоты расширения, в которой находится ячейка расширения памяти, тем выше приоритет доступа к её банкам ДОП. Другими словами признак активности установленный в "1" на ячейке с большим номером блокирует обращения в пределах данного сегмента не только к ООП, но и к ДОП с меньшим приоритетом.

В связи с необходимостью поддерживать гибкую архитектуру распределения памяти с учётом приоритетного доступа к ДОП, имеется несколько обязательных правил использования и установки ячеек расширения памяти Фг3. 089. 170:

порядок установки ячеек от младших номеров слот расширения к старшим, т.е. первая ячейка должна устанавливаться во вторую слоту (Х2), вторая - в третью (Х3), и т.д.;

между ячейками могут находиться другие модули расширения только, если на них имеются замкнутые между собой контакты А24 и Б24;

ячейки, устанавливаемые в слоты с большим номером имеют более высокий приоритет;

установленный в "1" признак активности на данном сегменте банка ДОП с более высоким приоритетом, в пределах адресов указанного сегмента;

при необходимости доступа к ДОП с более низким приоритетом в пределах адресов определённого сегмента, необходимо снять признаки активности с более высокими приоиртетами, а для доступа к ООП - все установленные прзнаки активности.

4.2.4. ПЗУ и псевдо - ПЗУ.

Как было указано ранее, адреса D000 - FFFF в адресном пространстве ЦП отводятся под системное ПЗУ. Использование этой части адресного пространства возможно в двух режимах:

в режиме обычного ПЗУ, когда на эти адреса подключено реальное ПЗУ, реализованное на микросхемах;

в режиме псевдо - ПЗУ, когда на эти адреса подключается часть оперативной памяти, блокируя при этом чтение из микросхем ПЗУ.

ПЗУ на микросхемах доступно всегда сразу после включения питания. В базовом исполнении это специальное стартовое ПЗУ имеет ограниченный объём - 2К байт, занимает самые старшие адреса F800-FFFF и содержит минимально необходимые программные средства, обеспечивающие выполнение следующих функций:

установка начального распределение памяти;

установка начального положения памяти экрана в режиме Т32 на третьей текстовой подстранице в адресах с 2000 - 27FF;

поиск контроллера НГМД и в случае обнаружения инициация начальной загрузки;

поддержка минимального диалога с пользователем в пределах функций описанных в общем техническом описании Фг3. 032. 002 ТО.

На особые свойства оперативной памяти доступной по адресам системного ПЗУ указывает само название - псевдо - ПЗУ. Оно означает, что в отличии от обычной оперативной памяти, оперативная память в режиме псевдо - ПЗУ может работать как ПЗУ, только на чтение, когда все попытки записать в неё данные, игнорируются. От обычного же ПЗУ её отличает наличие режима работы только на запись, когда происходит загрузка всей необходимой информации с последующим запретом на изменеия в режиме чтения. Такие свойства ориентированы на предоставление возможности пользования определённой части оперативной памяти для хранения системного программного обеспечения, предварительно однократно загруженного с ограниченными возможностями для случайного изменения в процессе дальнейшей работы. Соответственно это позволяет гибко изменять системное программное обеспечение в процессе эксплуатации ПЭВМ не прибегая каждый раз к изготовлению новых микросхем ПЗУ, а загружая соответствующее системное программное обеспечение со специальных системных дискетт.

Как уже упоминалось при обращении к ОП через адреса 6 сегмента есть особенность, заключающаяся в том, что из-за постоянного и неизменного наличия в адресах C000 - CFFF области ввода/вывода доступ к подключённому к этому сегменту банку памяти ёмкостью 8К разрешён только через адреса D000 - DFFF. С целью полного использования всей памяти ПЭВМ предусмотренатвозможность разделить банк, подключённый к 6 сегменту, на 2 части по 4К байт с возможностью подключения каждой из них к адресам D000 - DFFF.

Переключение псевдо - ПЗУ из режима в режим, а также подключение на адреса D000 - DFFF соответствующей части подключенного к сегменту 6 банка, осуществляется в режимах "АГАТ" и "Apple" по- разному. В режиме "АГАТ" для этого необходимо однократно выполнить команду записи по адресам указанным в табл. 1, после чего установится указанный в таблице режим. Текущее состояние режимов может быть определено при выполнении операции чтения по тем же адресам по состоянии разрядов D0,D1 и D3 шины данных в соответствии с табл. 1.

В режиме "Apple" управление псевдо - ПЗУ осуществляется аналогично, но только выполнением операций чтения по адресам С080-С0ВF в соответствии с табл. 2.

Примечание. Обозначения вида С083 С083 предполагают обязательное двукратное выполнение операции чтения по адресу С083.

Кроме двукратного чтения, к особенностям работы псевдо-ПЗУ в режиме "Apple" следует отнести режим, когда запрещено и чтение и запись. Данные особенности сохранены по соображению обеспечения совместимости со специальной платой расширения оперативной памяти, известной в системе Apple II, под названием "Language Card". Единственное отличие работы псевдо - ПЗУ в ПЭВМ "АГАТ" от "Language Card" заключается в том, что при переключениях, выполняемых по командам чтения на шине данных (на разрядах D3, D1, D0) присутствует предыдущее состояние.

4.3. Дисплейный контроллер.

Основное назначение дисплейного контроллера - отображение информации на экране видеоманитора. Процесс формирования изображения дисплейным контроллером основывается на растровом (или как его ещё называют растровом телевизионном) принципе развёртки изображения, что предопределяет жёсткую последовательность работы всех функциональных узлов ДК. Поэтому, чтобы была однозначность в понимании любых вопросов связанных с отображением информации в ПЭВМ, необходимо напомнить основные положения растрового принципа развёртки, лежащего в основе всех процессов формирования изображения дисплейным контроллером ПЭВМ "АГАТ":

изображение на экране складывается из последовательности отдельных кадров следующих с частотой кадровой развёртки равной 50 Гц (построчная развёртка), т.е. время развёртки одного кадра составляет приблизительно 20 мс;

каждый кадр изображения образуется из отдельных строк с последовательностью развёртки слева-направо, сверху - вниз;

частота строчной развёртки составляет 15625 Гц, то есть время развёртки одной строки 64 икс;

изображение формируется на экране в течение прямого хода луча по строке и по кадру: на время обратного хода луча, в течение которого происходит возврат луча в исходное положение, изображение гасится;

изображение формируется по мере продвижения луча (лучей) по по строке засветкой в нужный момент требуемых точек экрана заданным цветом.

Исходя из этих положений можно сформулировать основные задачи возлагаемые на ДК:

обеспечение синхронизации с ВКУ, формированием строчных и кадровых синхро - инпульсов требуемой частоты и длительности;

последовательное формирование адресов для обращения в нужную область памяти экрана по мере развёртки изображения;

преобразование информации поступающей из памяти в вид способный непосредственно управлять лучами ВКУ в соответствии с требуемым режимом отображения информации;

гашение изображения на время обратного хода луча по строке и по кадру, то есть формирование рабочего поля экрана в соответствии с требуемым форматом.

Процесс формирования изображения исплейным контроллером определяется также и особенностями каждого из требуемых режимов отображения информации, которые наряду с основными параметрами определяют, где, и в каком порядке в памяти экрана хранится информация об изображении, каким образом, считанная из памяти информация трансформируется в изображение, как задаётся цветовая окраска изображения.

4.3.1. Режимы отображения информации на экране.

Содержимое любой части оперативной памяти (исключения будут оговорены отдельно)) может быть отображено на экране видеомонитора в одном из 9 возможных режимов отображения. Размер отображаемой области ОП (памяти экрана) зависит от режима отображения. Основные характеристики режимов приведены в табл. 3.

4.3.2. Отображение информации в режиме "АГАТ".

4.3.2.1. Цветные графические режимы.

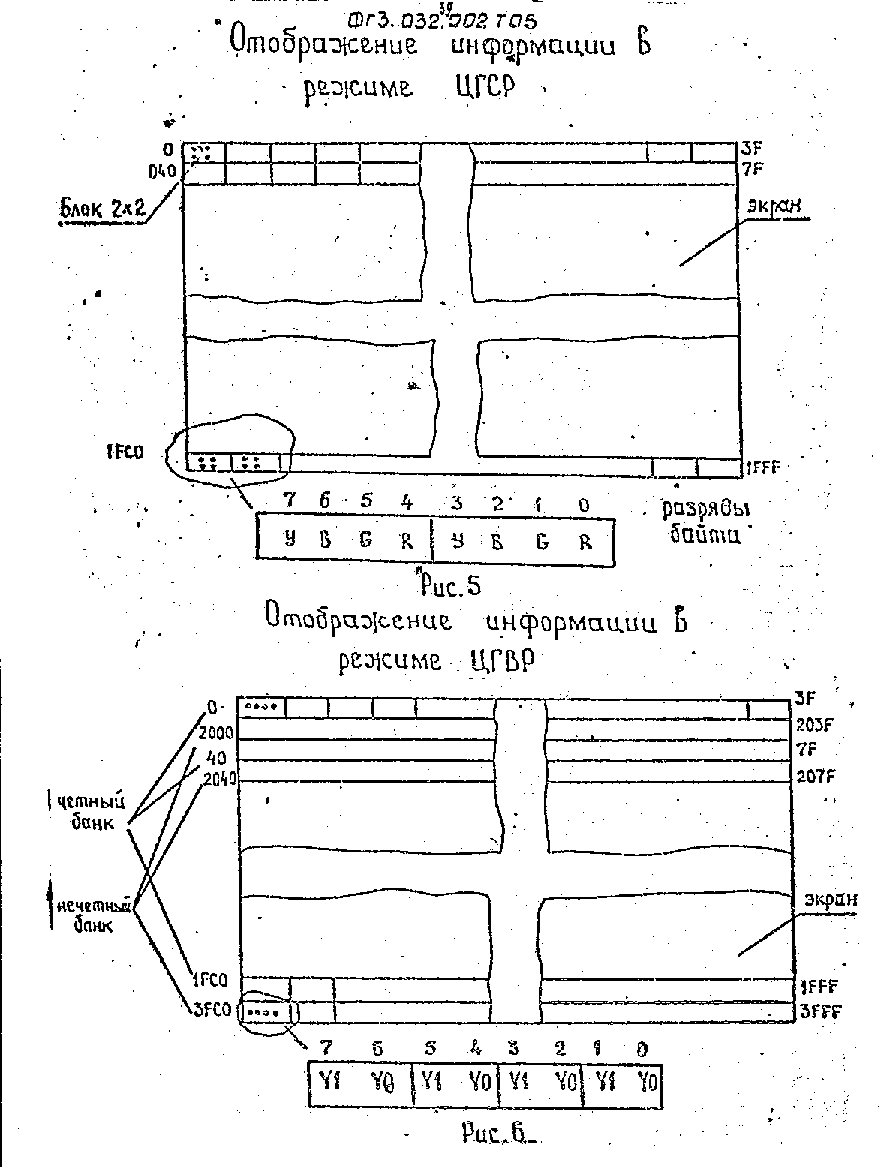

Дисплейный контроллер в режиме АГАТ имеет два цветных графических режима: среднего (ЦГСР) и высокого (ЦГВР) разрешения.

Режим ЦГСР иногда называют псевдографическим, т.к. элементом разложения в этом режиме является не точка, а некоторая совокупность точек, размером 2х2, высвечиваемая на экране одним цветом и получившая название блок (pixel). Формат изображения на экране: 128 строк по 128 блоков в строке. В этом случае каждый байт в памяти экрана разделяется на две тетрады, которые содержат код цвета соответствующего блока. Старшая тетрада первого байта экранной строки (разряды 4-7) содержит код цвета блока, расположенного с левого края экрана. Младшая тетрада (разряды 0-3) содержит код цвета следующего по строке блока и т.д. Для отображения одной строки блоков требуется 64 байта. Выборка информации из памяти экрана строго последовательна: первые 64 байта хранят информацию для первой строки блоков, вторые 64 байта - для второй строки т.д. Для отображения одного полного кадра требуется память экрана общим объёмом в 8К байт (рис.5). Четыре разряда для кодирования цвета позволяют иметь для каждгог блока 16 различных цветов. Возможные цвета и их кодировка приводятся в табл. 4.

Цветной графический режим высокого разрешения (ЦГВР) обеспечивает отображение в пределах рабочего поля экрана 65384 точек в виде матрицы из 256 рядов по 256 точек в ряду (рис.6). Каждой точке изображения на экране соответствуют два бита в памяти экрана. Каждый байт в памяти экрана хранит 2-разрядные коды для засветки 4-х точек. Старшие два разряда (6,7) первого байта экранной строки задают код цвета точки расположенной с левого края экрана. Разряды 4,5 задают код цвета следующей точки и т.д. Для отображения одной строки требуется 64 байта. Для отображения одного полного кадра требуется 16К байт памяти экрана, которая разделяется на две равные части соответствующие двум соседним банкам физической оперативной памяти. Банк с чётным номером (0, 2 и т.д.) обеспечивает хранение чётных строк развёртки, а банк с нечётным номером (1, 3 и т.д.) - нечётных строк. Два разряда кода цвета дают возможность высвечивать точки в 4-х цветах. Соответствие цветов отображаемых на экране точек кодам цвета в памяти экрана (палитру) можно прграммно изменить. Всего имеется четыре палитры. Цвет точки в зависимости от палитры приведён в табл. 11.

4.3.2.2. Монохромные графические режимы.

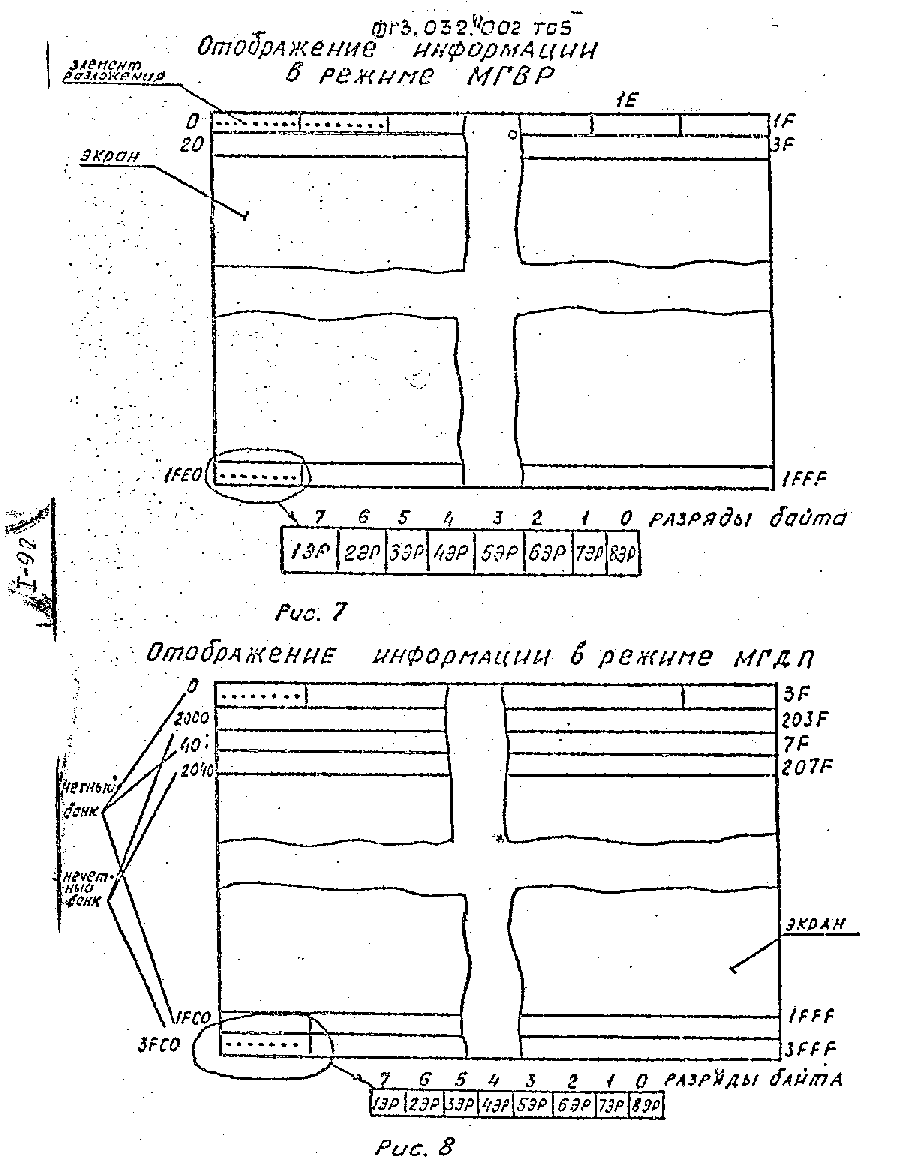

Монохромных графических режимов также два: монохромный графический режим высокого разрешения (МГВР) и монохромный режим удвоенной плотности (МГДП).

Режим МГВР имеет такой же формат изображения, что и цветной графический режим высокого разрешения 256х256. Но в этом режиме, в отличие от режима ЦГВР, каждой точке на экране соответствует не два бита в памяти экрана, а всего лишь один. "1" высвечивает соответствующую точку цветом, указанном в табл., а "0" гасит её (выводит в цвете фона). Соответственно вдвое уменьшается и объём памяти экрана: для отображения одной экранной строки требуется 32 байта и 8К байт на один полный кадр. Старший разряд (7) первого байта экранной строки отображается с левого края экрана, следующий отображается шестой разряд и т.д. За последним нулевым разрядом первого байта отображается старший разряд следующего байта и т.д. до нулевого разряда последнего 32-го байта строки (рис.7). Состояние каждого бита в памяти экранр определяет цвет засветки точки на экране в зависимости от палитры в соответствии с табл. 11.

4.3.2.3. Текстовые режимы.

Работа ДК в этих режимах основывается на традиционном знакоместным методе формирования изображения с использованием ПЗУ знакогенератора. В этих режимах всё рабочее поле экрана разбивается на знакоместа размером 7х8 (8 строк по 7 точек в строке). На каждом знакоместе может быть расположен либо один алфавитно - цифровой символ, размер которого составляет обычно 5х7 точек, либо графический символ размером, равным размеру знакоместа (7х8). Полиграммы (точечные матрицы) символов хранятся в ПЗУ знакогенератора. В памяти экрана хранятся только коды техсимволов, вывод которых предполагается на соответствующих знакоместах. Набор и количество возможных символов определяется объёмом ПЗУ знакогенератора и числом разрядов, используемых для задания кода различных символов. Набор символов и их коды приводятся в табл. 5.

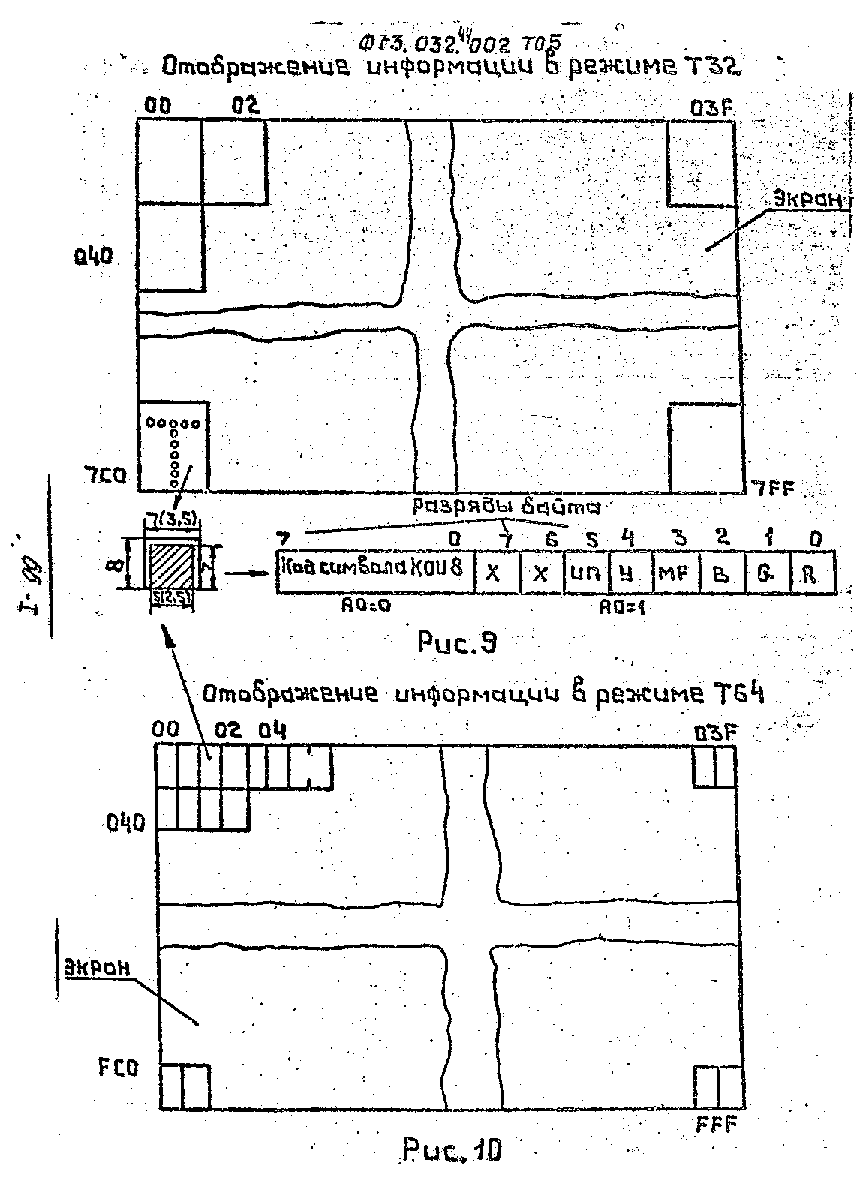

В цветном текстовом режиме (Т32) каждому знакоместу экрана соответствуют 2 байта в памяти экрана (рис. 9). На экране при этом располагается 1024 знакоместа ( 32 строки по 32 символа). Первый (чётный) байт, когда А0=0, содержит код символа, по КОИ-8, который должен быть выведен на данном знакоместе. Второй (нечётный) байт, когда А0=1, содержит следующую управляющую информацию:

R , G, B ( 0,1 и 2,0-ой биты) - разряды кода цвета символа. Четыре палитры позволяют менять цвет фона в соответствии с табл. 11;

ИП ( 5-ый бит) - разряд инверсии подсвета, задаёт режим вывода символа на экран: нормальный или инверсный. Нормальный символ выводится на тёмном фоне тем цветом, код которого задан в разрядах цвета. Инверсный символ выводится чёрным на фоне цветного знакоместа, цвет которого задан теми же разрядами цвета;

МЕ (3-ий бит) - разряд мерцания, задаёт режим мерцания, в котором символ отображается поочерёдно то инверсным, то нормальным с частотой переключения около 5 Гц.

Режимы отображения символа на экране в зависимости от состояния этих разрядов приведены в табл. 6.

В монохромном текстовом режиме (Т64) на экран выводится 2048 символов ( 32 строки по 64 символа). При этом, соотношение между форматом знакоместа и символа, остаётся прежним, а точка изображения на экране имеет вдвое меньший размер по строке (рис. 10). Это достигается увеличением тактовой частоты вывода символов до 10,5 МГц. Каждому знакоместу на экране соответствует один байт в памяти экрана (код КОИ-8 выводного символа). Цвет выводимых символов определяется палитрой по табл. 11.

4.3.3. Отображение информации в режиме "Apple".

4.3.3.1. Расположение памяти экрана в адресном поле ЦП.

Память экрана в режиме ПЭВМ Apple II состоит из 2-х частей, каждая из которых занимает свою отдельную фиксированную зону в адресном пространстве. Первая часть представляет собой память экрана для отображения информации в текстовом режиме. В адресном пространстве ЦП она занимает адреса 400-BFF:

400-7FF - первая страница;

800-BFF - вторая страница.

Вторая часть обеспечивает хранение информации для отображения в режиме HGR и также объединяет две страницы:

2000-3FFF - первая страница;

4000-5FFF - вторая страница.

Любая из страниц может быть использована для отображения одного полного кадра изображения. При этом часть памяти из адресного пространства каждой страницы не используется для целей отображения: из общего объёма памяти в 8К байт для каждой страницы, используется в качестве памяти экрана только 7,5К байт.

4.3.3.2. Графический режим высокого разрешения.

Этот режим можно было бы отнести к традиционным методам побитовой (поэлементной) графики, если бы не его спецефические особенности. Эти особенности настолько существенны, что можно выделить этот режим в самостоятельную разновидность методов побитовой графики: метод побитовой графики с цветовыми ограниченичми. Т.к. этот метод впервые был использован в ПЭВМ Apple II , то его также можно было бы назвать методом Apple II.

Суть данного метода состоит в том, что цвет отдельных точек изображения зависит не только от информации хранящейся в памяти экрана, но и от нескольких дополнительных факторов:

от местоположения точки на экране (чётная или нечётная колонка);

от кода одного невысвечиваемого бита для каждой группы из 7-и точек;

от засветки соседних точек справа и слева.

Основное преимущество такого метода заключается в экономии памяти экрана. Легко подсчитать, что для формирования изображения традиционными методами побитовой графики форматом 280х192 с 6-ю цветами на точку, требуется 20К байт памяти экрана. Это более чем в 2,5 раза больше требуемого объёма по методу Apple II.

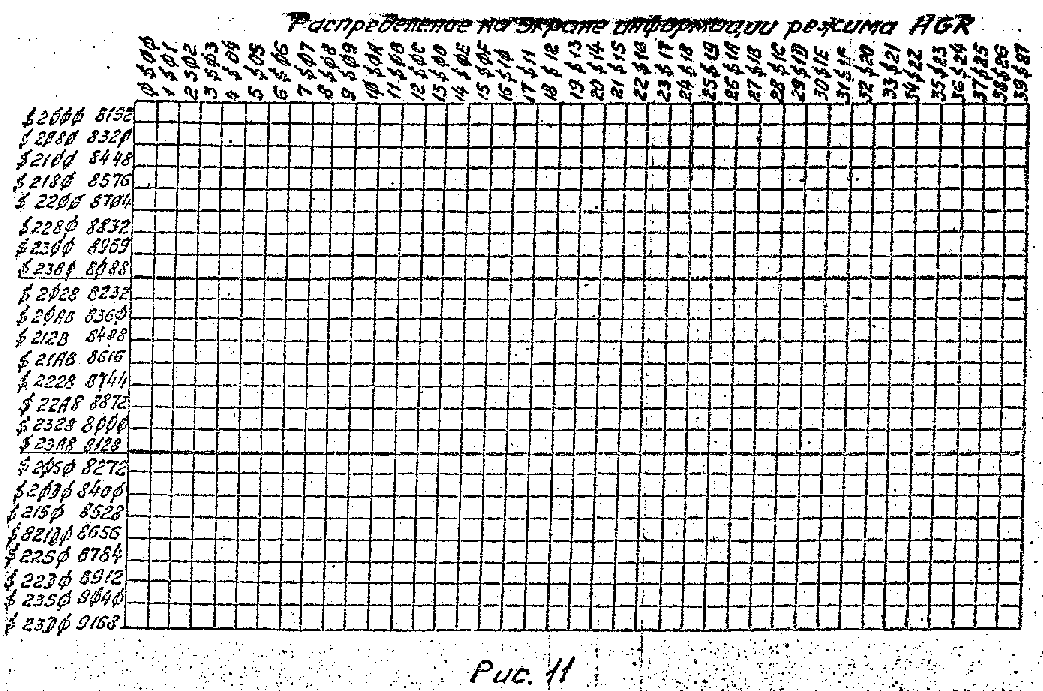

Для режима HGR порядок расположения на экране информации, хранимой в памяти, иллюстрируется на рис.11. Отображаемая страница памяти экрана (первая или вторая) разбивается на 8 областей по 1К байт каждая. Первая область обеспечивает хранение инфомации для 24-х строк изображения, вторая область содержит информацию для следующих 24-х строк и т.д. В пределах первой области (адреса 2000-23FF) информация располагается следующим образом:

первые 40 байт задают первую телевизионную строку (адреса 2000-2027);

вторые 40 байт задают 65-ую строку (2028-204F);

следующие 40 байт задают 129-ую строку (2050-2077);

8 байт для целей отображения не используются (2078-207F);

40 байт - 9-ая строка (2080-20А7);

40 байт - 73-я строка (20А8-20СF);

40 байт - 137-ая строка (20D0-20F7);

8 байт для отображения не используются (20F8-20FF) и т.д.

В пределах следующей области (адреса 2400-27FF) хранится информация о следующих 24 строках изображения:

40 байт задают 2-ю строку (2400-2427);

40 байт - 66-ая строка (2428-244F);

40 байт - 130-ая строка (2450-2477);

8 байт не используются (2478-247F);

40 байт - 10-ая строка (2480-24А7);

40 байт - 74-ая строка (24А8-24 СF);

40 байт - 138-ая строка (24D0-24F7);

8 байт не используются (24F8-24FF) и т.д.

Чтобы получить адрес любого отображаемого на экране байта, необходимо сложить следующие адреса (см рис.11):

адрес строки в пределах младшей области памяти экрана - адресах 2000-23F7 задающих строки 1, 9, 17, 25, 33 и т.д.;

адрес байта в пределах адресов строки - 40 байт (00-27);

адрес области памяти экрана в соответствии с табл.7.

4.3.3.3. Текстовый режим.

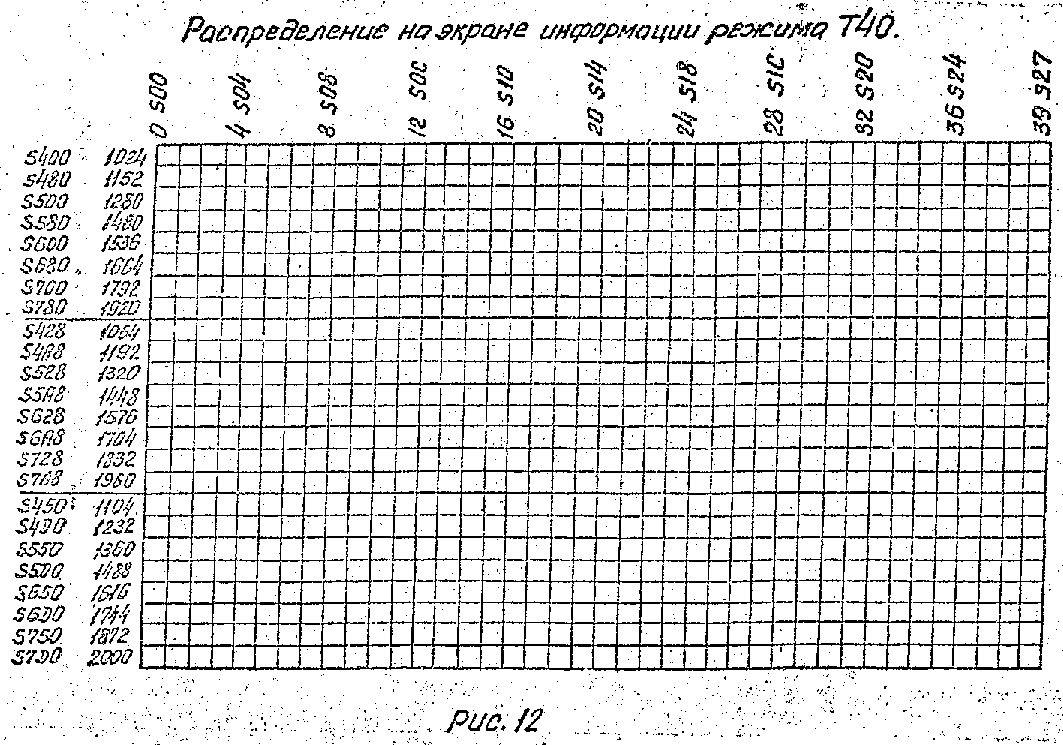

В текстовом режиме "Apple" (Т40) на экран выводится 24 строки по 40 символов. В пределах одной страницы информация из памяти экрана располагается следующим образом (рис.12):

первые 40 байт задают первую строку символов ( адреса 400-427);

вторые 40 байт задают 9-ую строку символов (428-44F);

следующие 40 байт задают 17-ую строку символов (450-477);

8 байт не используются (478-47F);

40 байт - 2-ая строка (480-4А7);

40 байт - 10-ая строка (4А8-4СF);

40 байт - 18-ая строка (4D0-4F7);

8 байт не используются (4F8-4FF) и т.д.

В этом режиме работы ДК используется тот же самый знакоместный метод, что и в текстовых режимах Т32 и Т64, при котором каждому байту в памяти экрана соответствует одно знакоместное на экране. Изображение на экране формируется с использованием того же ПЗУ знакогенератора. Но в отличие от текстовых режимов "АГАТ", в этом режиме разряды ИП и МЕ, задающие режим мерцания и инверсии символа, указываются вместе с кодом символа в одном байте. В младших разрядах байта указывается код символа, а в двух старших коды ИП и МЕ. Набор и количество возможных отображаемых символов приводятся в табл. 8.

Режим вывода символов задаётся двумя старшими разрядами в каждом байте памяти экрана - ИП (7 разряд) и МЕ (6 разряд). В зависимости от состояния этих разрядов возможен один из трёх режимов отображения символа на экране, соответствующих табл. 6. Цвет символа, или соответственно фона, задаются указанием палитры в соответствии с табл.11.

Символы русского языка выводятся только в нормальном режиме.

4.3.3.4. Смешанный режим.

В смешанном режиме изображение на экране разделяется на две части. Формирование изображения в верхней части осуществляется в графическом режиме HGR. В нижней части выводятся 4 полных строки текста. Процесс развёртки изображения в пределах каждой части происходит согласно правилам вывода изображения соответствующего режима. Формат графической части составляет - 280х160 точек.

4.3.4.1. Переключение режимов отображения "АГАТ"

Таблица 9

----------------------------------------------------------

разряды ША ! Выполняемая функция

---------------------------------------------------------

А7 ! признак удвоенной плотности (МГДП или Т64)

А6 ! ЭС2

А5 ! ЭС1 экранные страницы

А4 ! ЭС0

А3 ! ЭПС1 (текст) или ЭС3 (графика)

А2 ! ЭПС0 (текст); в графике несущественен

А1 ! РВИ2 00-ЦГВР 10-Т32 или Т64

А0 ! РВИ1 01-ЦГСР 11 МГВР или МГДП

------------------------------------------------------------

Таблица 10

------------------------------------------------------------

Номер! Программные переключатели !Номер

ЭС и ! ! ! ! !Номер! ! !экрана

банка! ЦГВР ! МГДП ! ЦГСР ! МГВР ! ЭПС ! Т32 ! Т64 !текста

-----!------!------!------!------!-----!------!------!------

! ! ! ! ! 0 ! C702 ! C782 ! 0

! ! ! ! ! 1 ! C706 ! C786 ! 1

0 ! ! ! C701 ! C703 ! 2 ! C70A ! C78A ! 2

! ! ! ! ! 3 ! C70E ! C78E ! 3

-----! C700 ! C780 !------!------!-----!------!------!------

! ! ! ! ! 0 ! C712 ! C792 ! 4

! ! ! ! ! 1 ! C716 ! C796 ! 5

1 ! ! ! C711 ! C713 ! 2 ! C71A ! C79A ! 6

! ! ! ! ! 3 ! C71E ! C79E ! 7

-----!------!------!------!------!-----!------!------!------

! ! ! ! ! 0 ! C722 ! C7A2 ! 8

! ! ! ! ! 1 ! C726 ! C7A6 ! 9

2 ! ! ! C721 ! C723 ! 2 ! C72A ! C7AA ! A

! ! ! ! ! 3 ! C72E ! C7AE ! B

-----! C720 ! C7A0 !------!------!-----!------!------!------

! ! ! ! ! 0 ! C732 ! C7B2 ! C

! ! ! ! ! 1 ! C736 ! C7B6 ! D

3 ! ! ! C731 ! C733 ! 2 ! C73A ! C7BA ! E

! ! ! ! ! 3 ! C73E ! C7BE ! F

-----!------!------!------!------!-----!------!------!------

! ! ! ! ! 0 ! C742 ! C7C2 ! 10

! ! ! ! ! 1 ! C746 ! C7C6 ! 11

4 ! ! ! C741 ! C743 ! 2 ! C74A ! C7CA ! 12

! ! ! ! ! 3 ! C74E ! C7CE ! 13

-----! C740 ! C7C0 !------!------!-----!------!------!------

! ! ! ! ! 0 ! C752 ! C7D2 ! 14

! ! ! ! ! 1 ! C756 ! C7D6 ! 15

5 ! ! ! C751 ! C753 ! 2 ! C75A ! C7DA ! 16

! ! ! ! ! 3 ! C75E ! C7DE ! 17

-----!------!------!------!------!-----!------!------!------

! ! ! ! ! 0 ! C762 ! C7E2 ! 18

! ! ! ! ! 1 ! C766 ! C7E6 ! 19

6 ! ! ! C761 ! C763 ! 2 ! C76A ! C7EA ! 1A

! ! ! ! ! 3 ! C76E ! C7EE ! 1B

-----! C760 ! C7E0 !------!------!-----!------!------!------

! ! ! ! ! 0 ! C772 ! C7F2 ! 1C

! ! ! ! ! 1 ! C776 ! C7F6 ! 1D

7 ! ! ! C771 ! C773 ! 2 ! C77A ! C7FA ! 1E

! ! ! ! ! 3 ! C77E ! C7FE ! 1F

-----!------!------!------!------!-----!------!------!------

8 ! ! ! C709 ! C70B !

-----! C708 ! C78B !------!------!

9 ! ! ! C719 ! C71B !

-----!------!------!------!------!

A ! ! ! C729 ! C72B !

-----! C728 ! C7AB !------!------!

B ! ! ! C739 ! C73B !

-----!------!------!------!------!

C ! ! ! C749 ! C74B !

-----! C748 ! C7CB !------!------!

D ! ! ! C759 ! C75B !

-----!------!------!------!------!

E ! ! ! C769 ! C76B !

-----! C768 ! C7EB !------!------!

F ! ! ! C779 ! C77B !

----------------------------------

4.3.4.2. Управление режимами отображения "Apple"

4.3.5. Переключение цветовой палитры.

Таблица 11

--------------------------------------------------------

Режим ! Код ! Цвета в ! Цвета в ! Цвета в ! Цвета в

! цвета !палитре 1!палитре 2!палитре 3!палитре 4

! ! (C058/ ! (C059/ ! (C058/ ! (C059/

! ! C05A) ! C05A) ! C05B) ! C05B)

--------------------------------------------------------

!00 ! 0 ! черный ! белый ! черный ! черный

!01 ! 1 ! красный ! красный ! черный ! красный

ЦГВР !10 ! 2 ! зеленый ! зеленый ! зеленый ! черный

!11 ! 3 ! синий ! синий ! синий ! синий

--------------------------------------------------------

МГВР !00 ! 0 ! черный ! белый ! черный ! зеленый

МГДП !01 ! 1 ! белый ! черный ! зеленый ! черный

Т64,Т40! ! ! ! ! !

--------------------------------------------------------

Т32 ! - ! черный ! синий ! черный !фиолетовый

--------------------------------------------------------

4.4.1.4. Линии синхронизации

4.6.2. Организация приоритетного обслуживания ПДП